Research Objectives

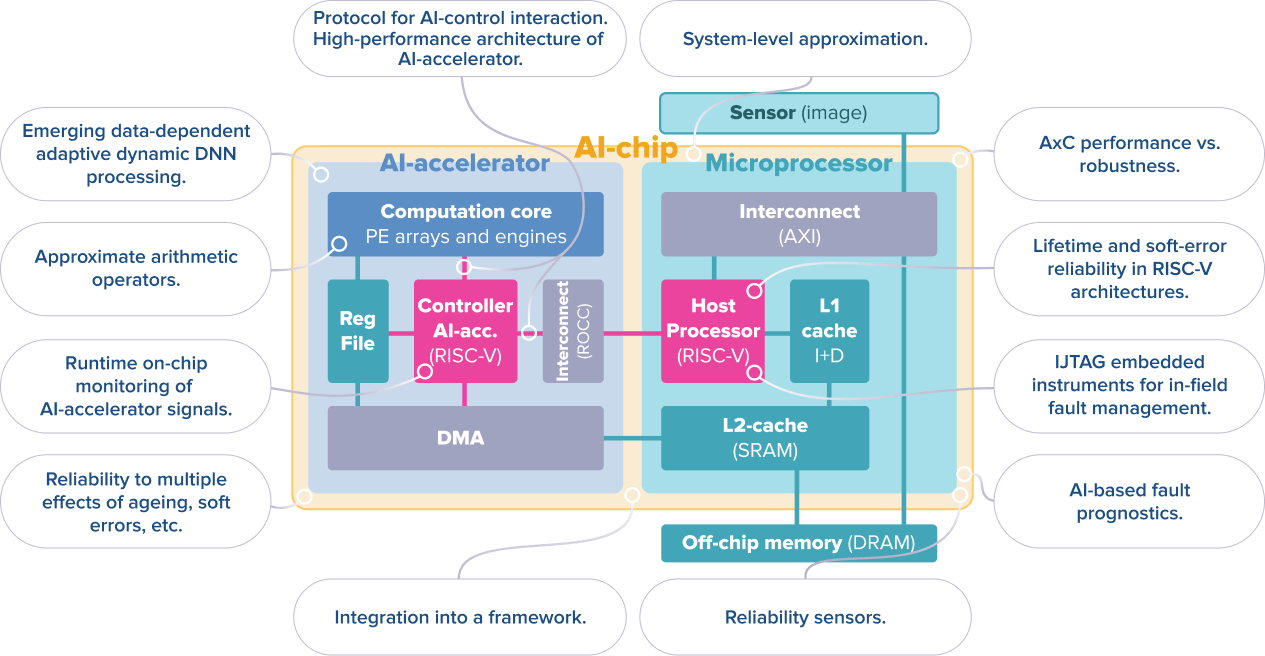

State of play. AI-chip designs incorporate specialised hardware accelerators optimised for AI workloads, enhancing computational efficiency and reducing power consumption. Techniques like approximate computing and dynamic neural networks help optimise models for deployment on hardware, reducing memory and computation requirements. The main control of the computation flow for the application is performed by a processor (e.g., open RISC-V designs). However, there is still a set of challenges for the efficiency and reliability of AI chips.

- AI-chip designs need to optimise power consumption to meet the energy efficiency demands of various applications, especially in resource-constrained devices like IoT and edge devices.

- Designing AI chips that scale efficiently with increasing model sizes and complexities requires considering the specific AI algorithms (e.g., dynamic neural networks) and tailoring the hardware accordingly.

- Efficiently managing memory bandwidth and reducing memory access latency is crucial for AI workloads, considering both data movement in and out of the chip (e.g., to DRAM) as well as within the chip (e.g., from the host processor to the AI accelerator computation cores).

- AI-chips need to be reliable against various sources of errors, including radiation, ageing, or hardware faults, to ensure trustworthy operation, especially in critical applications like healthcare and autonomous vehicles.

- Balancing performance and cost-effectiveness is vital to ensure the widespread adoption of AI-chips across various industries.

Beyond SOTA. TAICHIP addresses these challenges in a multidisciplinary approach involving expertise in computer architecture, reliability engineering, algorithm design, and domain-specific knowledge of AI applications. The action targets an R&D&I platform for efficient and reliable AI-chip design and TalTech’s collaboration in research with the Advanced Partners as a balanced combination of applied research and emerging research topics:

- Advanced AI-accelerator architectures (led by UOM, task T4.1)

- Open-source RISC-V based processor architectures (led by ETHZ, task T4.2)

- Efficiency optimisation of processor-accelerator pair (led by ECL, task T4.3)

- Reliable hardware for AI chip implementation (led by IHP, task T4.4)